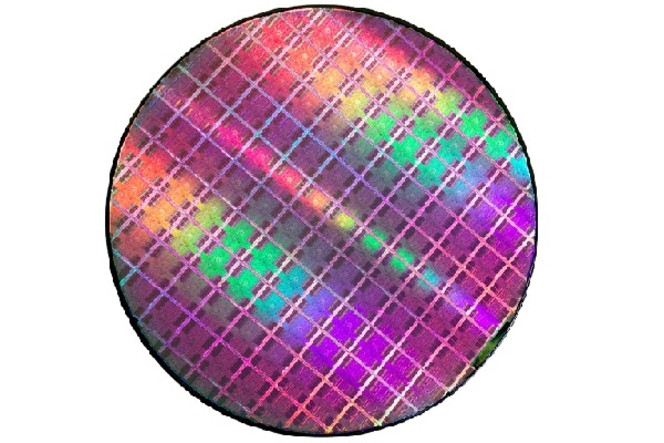

Alors que les processeurs mobiles les plus avancés sont gravés en 10 nm, les premères puces passant à une gravure en 7 nm, synonyme de plus grande compacité pour de meilleures performances et une consommation d'énergie réduite, sont attendues dès le second semestre chez TSMC (Apple A12, Kirin 980...)

Dans un communiqué, l'entreprise coréenne dévoile sa roadmap des étapes suivantes, présentée lors du Samsung Foundry Forum (SFF) 2018. Cela passera d'abord par un raffinement du 7LPP qui permettra de passer à une gravure en 5 nm, dite 5LPE (Low Power Early) avec des avantages sur la miniaturisation des composants et une consommation d'énergie encore plus faible.

Viendra ensuite la gravure en 4 nm déployée en deux évolutions, 4LPE d'abord puis 4LPP. On arrivera là aux limites des possibilités des transistors 3D dits FinFET et il s'agira là encore d'une optimisation poussée du 5LPE plutôt que d'une nouvelle technologie de gravure, ce qui veut dire aussi qu'elle sera plus facile à mettre en oeuvre.

Sous les 4 nm, changement de technologie

Pour aller plus bas encore, il faudra passer à une autre configuration que le FinFET pour le noeud de gravure. Ce sera l'approche GAA (Gate-All-Around) qui permettra de proposer de la gravure en 3 nm, en deux évolutions 3GAAE (E pour Early) et 3GAAP (P pour Plus).

Samsung indique être en train de développer une technologie spécifique, dite MBCFET (Multi-Bridge-Channel FET) pour dépasser les contraintes du FinFET à un tel noeud de gravure.

Mais, au-delà de la gravure en 7 nm programmée pour début 2019, le groupe coréen ne donne pas encore d'indications sur le timing de ces différentes avancées en matière de gravure de composants électroniques, ce qui suggère qu'il se laisse encore le temps d'adapter son effort face aux difficultés techniques et économiques (notamment avec l'évolution de l'indicateur du coût par transistor) qui s'annoncent.