Après les transistors planaires, le passage aux transistors 3D FinFET a permis d'exploiter des technologies de gravure descendant jusqu'à des noeuds d'une dizaine de nanomètres, actuellement utilisées pour les processeurs mobiles gravés en 14/16 nm et 10 nm.

S'il sera encore possible de s'appuyer sur cette expertise pour descendre jusqu'à 7 nm, la situation se compliquera par la suite avec les technologies actuelles, tant la finesse de gravure devient difficile à maîtriser.

S'il restera possible de réaliser de la gravure en 5 nm FinFET, le gain risque de ne plus être à la hauteur des contraintes techniques et physiques exigées et nécessitera de nouvelles approches.

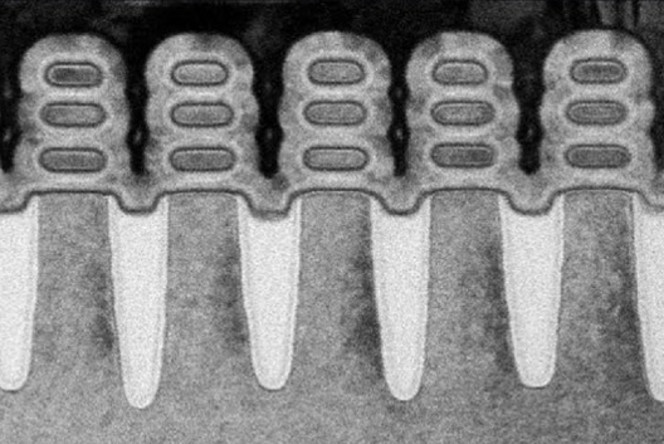

Les chercheurs d'IBM et de Globalfoundries annoncent donc avoir mis au point une architecture de transistors qui ouvre la voie à des composants gravés en 5 nm offrant de meilleures performances que le FinFET.

L'architecture repose sur des transistors faits d'empilements de nanofeuilles de silicium, un sujet de recherche sur lequel IBM travaille depuis 10 ans et qui pourrait trouver ici une application en offrant plus d'efficacité que les transitors 3D, pouvant donner à terme des smartphones capables d'atteindre facilement deux à trois jours d'autonomie (contre une journée actuellement) et des améliorations de performances significatives dans des domaines exigeants comme l'intelligence artificielle ou la réalité virtuelle.

Un premier wafer de test gravé en 5 nm (source : IBM / Connie Zhou)

IBM affirme ainsi que des puces gravées en 5 nm selon sa technique offriraient une amélioration de performances de 40% mais une réduction de la consommation d'énergie de 75% par rapport à des puces gravées en 10 nm FinFET telles que produites actuellement.

Le processus de gravure exploite la même lithographie EUV (Extreme Ultra Violet) qui sera utilisée par Globalfoundries pour proposer des puces gravées en 7 nm FinFET à partir de 2018.

L'annonce de transistors en nanofeuilles de silicium veut aussi montrer qu'il sera possible d'ici quelques années de placer quelque 30 milliards de transistors dans une simple puce, contre 20 milliards pour une puce gravée en 7 nm.