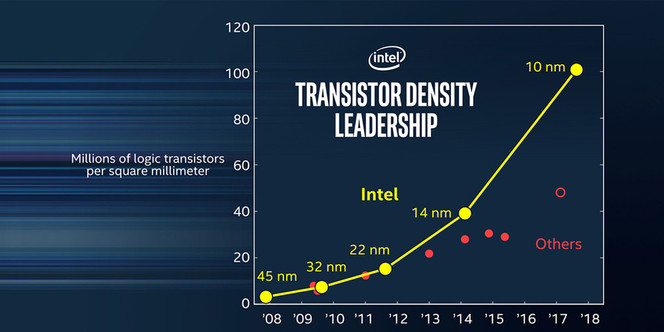

Le groupe Intel a vu passer devant les fondeurs Samsung et TSMC en matière de gravure en 10 nm. Les deux entreprises asiatiques ont déjà démarré la production de masse (peut-être avec quelque retard et des problèmes de rendement initiaux) tandis que le géant américain ne se lancera que plus tard cette année.

Et puisqu'il ne peut pas lutter sur la disponibilité, le groupe de Santa Clara joue la carte de la qualité en affirmant que sa technologie de gravure en 10 nm sera bien plus performante et beaucoup moins coûteuse que celle de ses rivaux.

Il affirme ainsi être devant sur les différents aspects techniques avec un avantage de coût de l'ordre de 30%. Intel redit encore une fois pour l'occasion que la loi de Moore reste valide pour ce noeud de gravure, avec une densité de transistors multipliée par 2,7 par rapport à la génération précédente (la gravure en 14 nm), permettant de rassembler 100 millions de transistors par mm2 (soit environ le double de ce que proposeraient Samsung et TSMC), même si le 10 nm met un peu plus de temps que prévu à être lancé.

Intel en profite pour appeler à une nouvelle nomenclature reflétant mieux les avancées réalisées à chaque noeud de gravure plus fin, accusant implicitement ses concurrents d'affiner leurs circuits sans apporter d'évolution significative aux process et de s'écarter ainsi, eux, de la loi de Moore.

Les premières puces Intel Cannonlake arriveront ainsi durant le second semestre 2017, trois ans après le lancement de la gravure en 14 nm.

Elle exploitera la troisième génération de transistors 3D FinFET (anciennement Tri-Gate lors de leur annonce en 2011) et exploitera un gate pitch de 54 nm (contre 70 nm pour le 14 nm), le plus fin du marché et en avance d'une génération par rapport aux solutions concurrentes, affirme encore Intel.