La loi de Moore est simple, et jusqu'ici elle était relativement réalisable par les fondeurs de puces informatiques, elle indiquait que le nombre de transistors par puce double tous les 12 mois et que chaque nouveau transistor coute aussi cher que le précédent.

Pendant des années, cette intuition s'est confirmée : les processeurs évoluent sur des rythmes allant de 6 à 12 mois avec un accroissement du nombre de transistors, pour des prix qui restent stables... Et pourtant, il semble que nous soyons arrivés à un palier qui met en défaut la loi de Gordon Moore.

Selon Peter Bright, de Arstechnica, "Atteindre l'objectif n'est pas arrivé par accident". Soit, les spécialistes du secteur se sont organisés, et planifié des développements et des feuilles de route sur plusieurs années pour tenir ces délais de 12 mois et obtenir des processeurs à la capacité doublée.

En 1975, Gordon Moore revenait sur sa formulation en doublant le temps nécessaire à 24 mois.

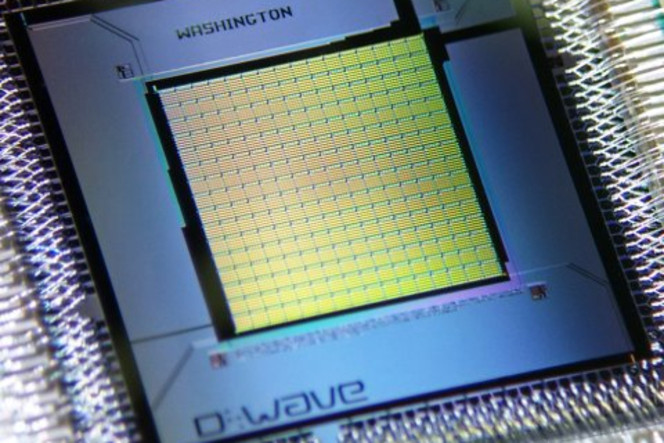

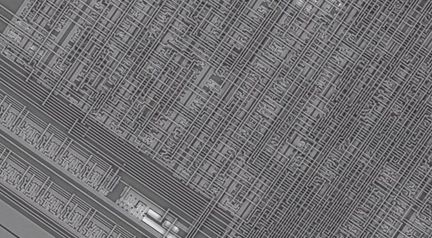

Mais depuis, les constructeurs se sont lancés dans une course différente de celle de la puissance brute : la miniaturisation. Et cette miniaturisation impose des limites et le doublement des capacités des processeurs ne semble plus possible.

La prochaine feuille de route officielle qui sera annoncée par l'ITRS (International Technology Roadmap for Semiconductors) s'écartera pour la première fois de la loi de Moore.

Intel a déjà annoncé indirectement qu'il ne serait pas possible d'atteindre ce type d'objectif à temps en évoquant le retard de la gravure en 10 nanomètres, désormais prévue pour le deuxième semestre 2017.

Même la révolution attendue dans la gravure, la technologie des 2 nanomètres avancée par les constructeurs et prévue pour 2020 semble désormais impossible à envisager, et il n'existe à ce jour aucune autre technologie alternative permettant d'atteindre cette précision.

Le nouveau secteur de progression est désormais celui de l'Internet des objets, et la conception de puces hautement intégrées ( associer directement un ensemble de composants dans une puce unique à l'image d'un SoC aux fonctionnalités plus poussées).