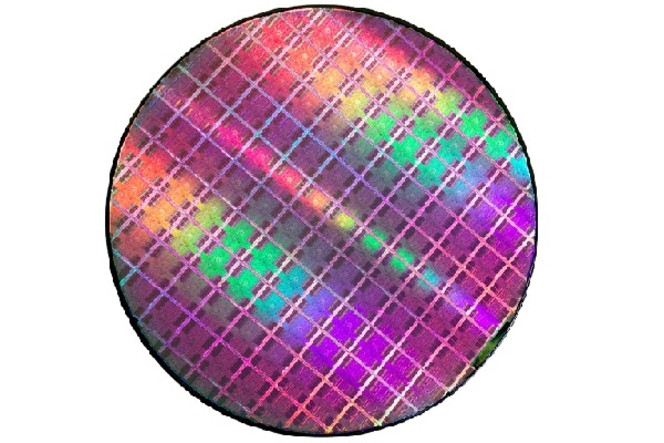

Si le concurrent TSMC a pris les devants en matière de gravure en 7 nm et récupéré tous les gros clients cette année, Samsung n'a pas dit son dernier mot et prépare sa propre technologie de gravure en 7 nm avec l'avantage de la lithographie EUV.

7 nm 7LPP

Samsung Foundry a déjà installé plusieurs machines EUV du fournisseur ASML sur son site coréen Fab S3 de Hwaseong qui doit accueillir un nouvelle aile spécifiquement conçue pour l'EUV, et prépare sa montée en production pour du 7LPP (7 nm Low Power Plus).

En attendant, la gravure en 10 nm n'a pas dit son dernier mot et Samsung prépare une optimisation 8LPU (8 nm Low Power Ultimate) sur les bases du 8LPP, lui-même une évolution du 10LPP.

8 nm 8LPU

Le 8LPU permettra vraisemblablement d'accroître encore un peu la densité en transistors par rapport au 8LPP. Ces deux technologies apportent des performances plus pointues que le 10LPP / 10 LPU pour des clients qui ne peuvent par ailleurs pas basculer vers de la gravure en 7 nm.

La mise en préproduction de la gravure en 8LPU est prévue cette année, ce qui devrait permettre de proposer la technologie dès l'an prochain.

Vers le 5 nm puis le 3 nm

Par la suite, Samsung pense déjà à la gravure en 5 et 4 nm avec des technologies 5LPE (Low Power Early), 4LPE et 4LPP programmées. Pour ce noeud de gravure, la firme continuera d'exploiter des technologies FinFET (transistors 3D) et la lithographie EUV.

La préproduction du 5 / 4 nm pourrait débuter dès 2019, ce qui tend à indiquer que la gravure en 5 nm pourra être proposée dans le même temps du cycle du 7 nm, et non à sa suite. On restera prudent sur ces timings prévisionnels, dans la mesure où les obstacles techniques ne sont pas tous résolus et tandis que les investissements deviennent très lourds.

Samsung Foundry commence même à évoquer de la gravure en 3 nm qui nécessitera d'abandonner le FinFET pour du GAAFET (Gate-All-Around) sur une base MBCFET (Multi-bridge-channel FET) donnant des gravures 3GAAE et 3GAAP.