Les détails sur ce futur processeur :

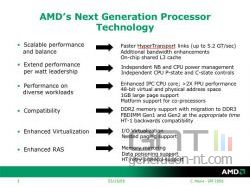

- 4 coeurs indépendants ( Intel juxtapose deux double-coeurs )

- 512 Ko de mémoire cache L2 pour chacun des processeurs

- 2 Mo de mémoire cache L3 partagés entre les différents processeurs

- Les ypes de mémoire supportées : DDR2, DDR3 et FB-DIMM

- Le support de l'HyperTransport 3.0 ( 5,2 Go/s )

- Avec adressage de la mémoire sur 48 bits

- Chacune des 4 puces gérera sa tension de fonctionnemment

Il faudra attendre jusqu'en 2007.

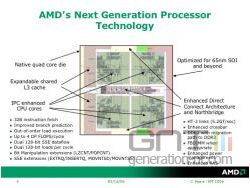

En effet, comme nous vous l'indiquions précédemment, ce seront les puces pour serveurs qui seront les premières à arriver. La première version débarquera au second semestre 2007. Nommée " Deerhound ", elle intégrera de la mémoire cache de second niveau, sera compatible avec la mémoire DDR2 et le socket F à 1207 broches. Elle bénéficiera d'une finesse de gravure à 65 nanomètres.

Une mise à jour des processeurs pour serveurs arrivera au cours du deuxième deuxième trimestre 2008. Il s'agira de " Zamora ". Cette dernière intégrera de la mémoire cache de troisième niveau, supportera la mémoire FB-DIMM et l'HyperTransport 3.0.

Enfin, au cours de cette même période, arrivera une version pour les machines serveurs / stations de travail. Baptisée " Cadiz ", celle-ci intègrera de la mémoire cache de second niveau, sera compatible avec les mémoires DDR2 et DDR3 et supportera l'HyperTransport 3.0.

Les processeurs pour machines de bureau n'arriveront, quant à eux, pas avant le premier semestre 2008. Appelés " Greyhound ", ils intégreront de la mémoire cache de second niveau, seront compatibles avec la DDR2 et la DDR3 et supporteront l'HyperTransport 3.0.

Merci à Sh4DO pour les deux plaquettes ci-dessus.