On a l'habitude voir les processeurs comme de petits composants électroniques intégrés dans les appareils, du smartphone au PC en passant par le serveur. Ils sont produits en nombre à partir de galettes de silicium, les wafers, qui sont ensuite découpées pour obtenir les puces à l'unité.

L'évolution des systèmes informatiques a généré de nouveaux besoins et les fondeurs se sont adaptés pour produire des composants regroupant plusieurs processeurs ou chiplets et toujours plus de composants mémoire, le tout fonctionnant en commun grâce à un interposeur.

Ces systèmes sont plus efficaces que des alignements de puces séparées, augmentant significativement les puissances de calcul tout en restant dans certaines limites d'encombrement, de complexité et de consommation d'énergie.

Les systèmes sur wafer, la prochaine évolution

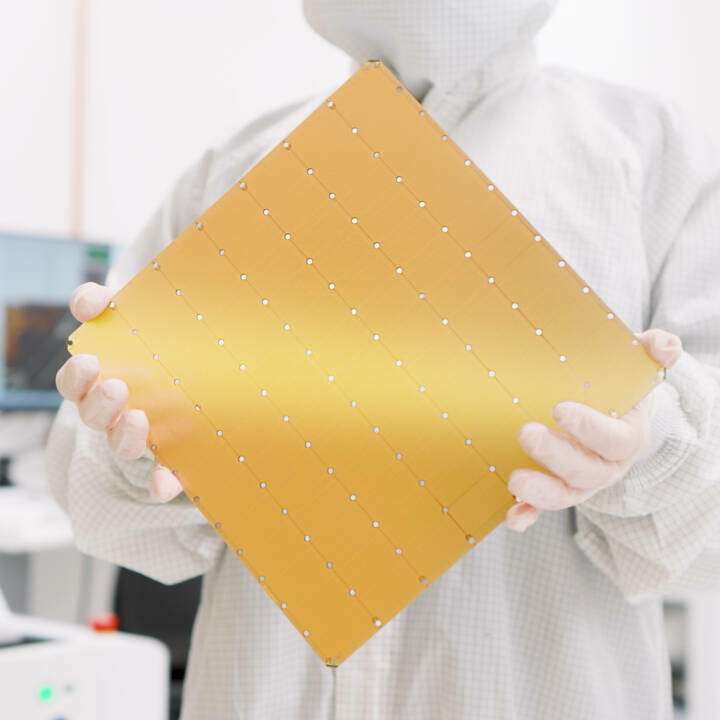

Mais il est possible d'aller encore plus loin et de faire d'un wafer entier une sorte de processeur géant, ou System on Wafer (WoS). La firme Cerebras en fait une spécialité avec son Wafer Scale Engine (WSE) dont l'actuelle troisième génération intègre près d'un million de coeurs gravés en 5 nm représentant 4000 milliards de transistors travaillant en commun et accompagnés d'une grosse quantité de mémoire pour les servir.

Cerebras WSE, une superpuce grande comme un wafer

De son côté, Tesla a aussi développé un système complet sur wafer pour son supercalculateur Dojo destinés à entraîner l'intelligence artificielle permettant la conduite semi-autonome et bientôt autonome de ses véhicules électriques.

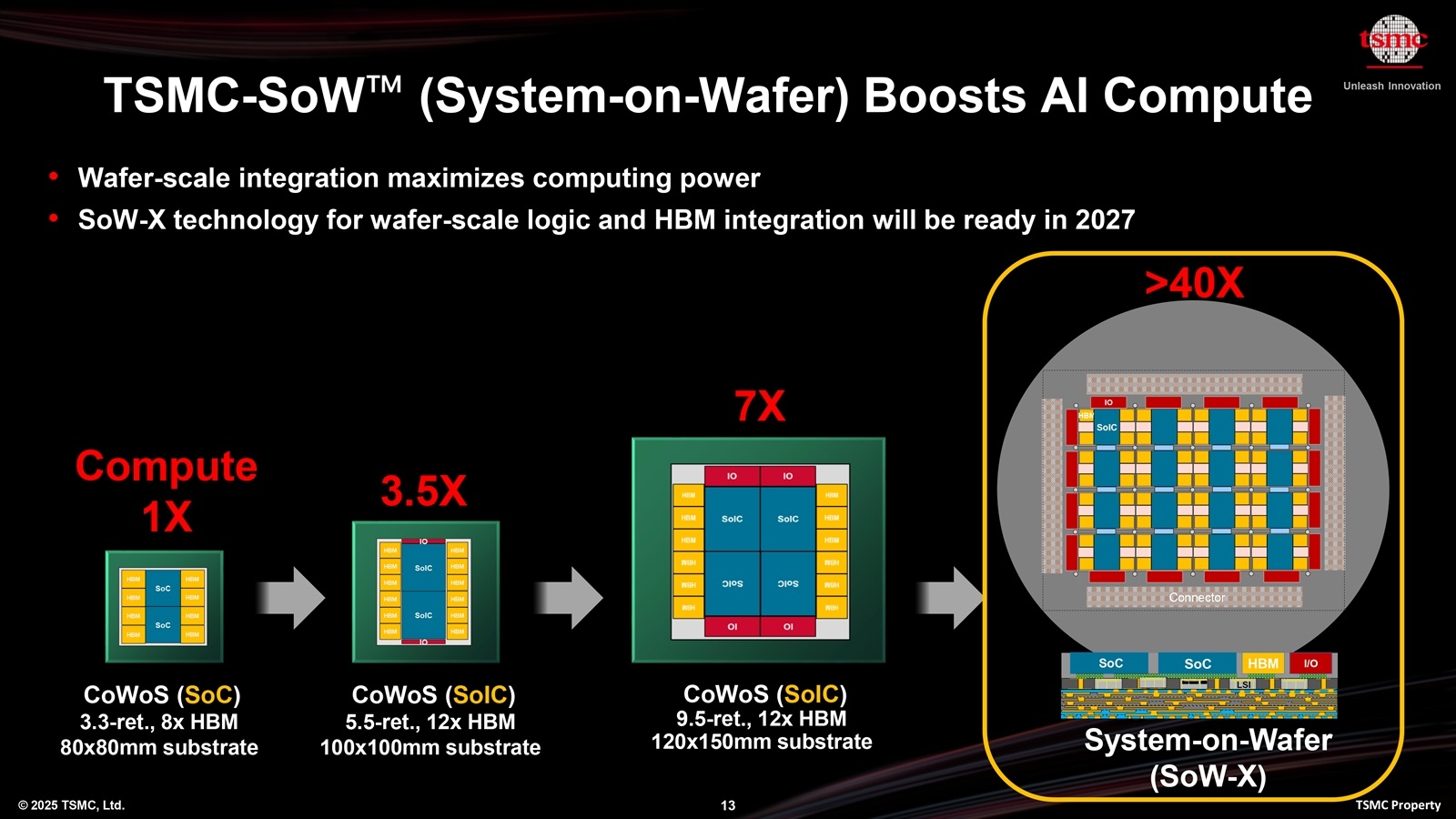

D'autres acteurs pourraient se mettre aux WoS prochainement, du fait de l'essor des grands centres de données IA et le fondeur taiwanais TSMC prépare un procédé standard SoW-X qui permettra de créer ces fameux processeurs géants occupant tout un wafer.

Avec un tel système, la puissance de calcul pourra être multipliée jusqu'à 40 fois par rapport à des puces simples avec là encore tous les composants fonctionnant de concert comme un unique processeur géant.

TSMC WoS-X, le procédé des superpuces pour datacenters IA

Le procédé de TSMC pourra accueillir des SoIC (System on integrated chip), puces aux composants empilés, supporter les procédés de gravure en 2 nm (N2) et 1,6 nm (A16) pour les chiplets et en 3 nm (N3) pour le die, accompagnés de 12 composants mémoire HBM4.

Cela représentera sans doute un coût conséquent par rapport à la production de puces séparées mais ce développement est sans doute en lien avec une demande des clients de TSMC et donc prêts à y mettre le prix pour disposer de ces superpuces à partir de 2027.

Pour rappel, TSMC est en train de lancer la production de masse pour la gravure en 2 nm et disposera du procédé A16 (gravure en 1,6 nm) d'ici fin 2026. Le fondeur prévoit par la suite de basculer vers le 1,4 nm (A14) à partir de 2028.