C'est logiquement (sauf nouveaux retards) cette année que l'interface PCIe 5.0 trouvera place dans des processeurs grand public, en l'occurrence les processeurs Intel Alder Lake, en fin d'année.

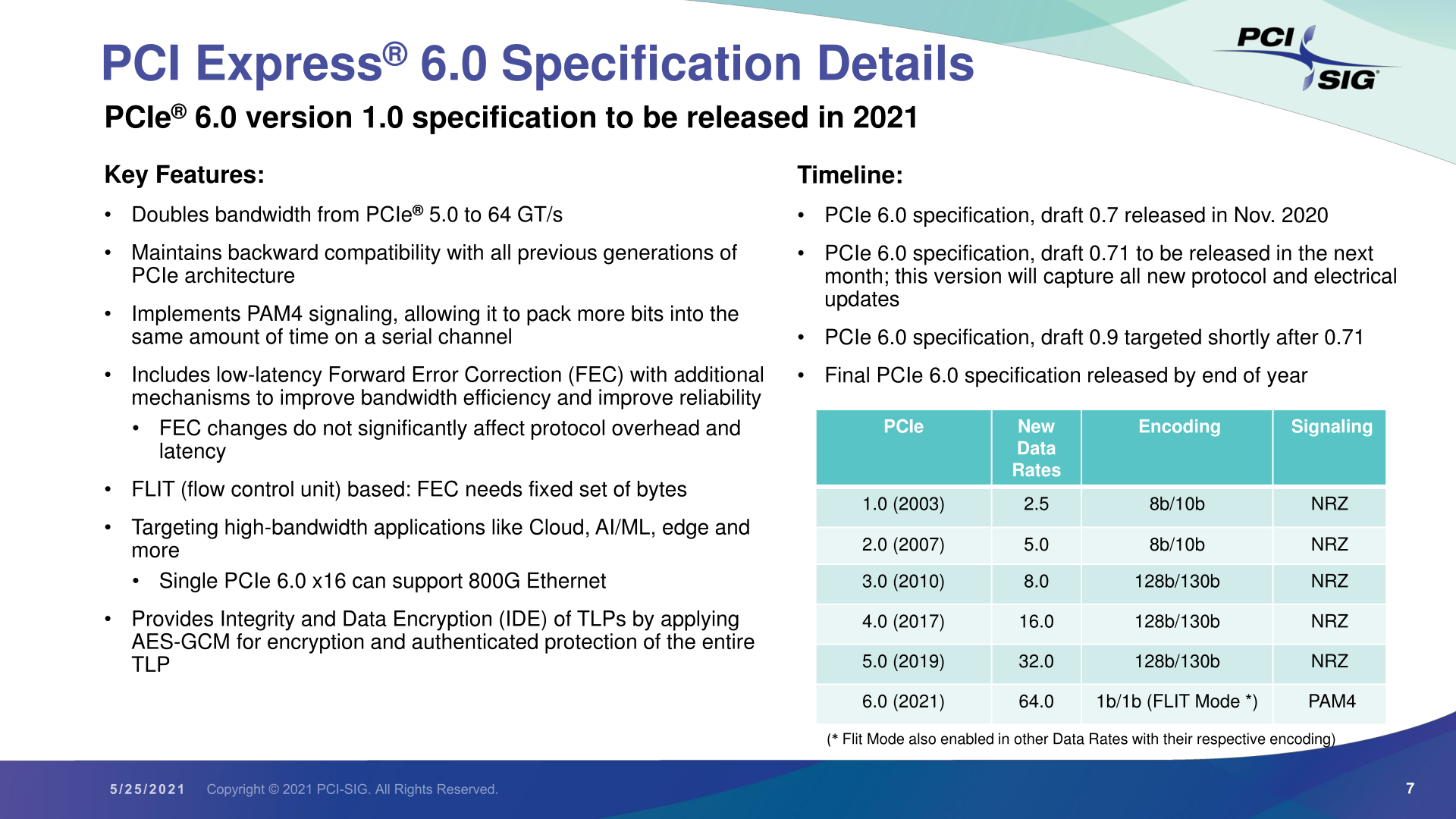

Dans le même temps, le groupe de promotion PCI-SIG poursuit ses travaux sur PCI Express 6.0 et fait un point d'étape sur sa finalisation. Car si la spécification est encore en version 0.7, c'est bien une version finale qui devrait être obtenue avant la fin de l'année, soit deux après PCIe 5.0.

Le groupe de promotion continue de recueillir les avis de ses membres avant de proposer une version 0.71 qui fixera un certain nombre de points. L'étape suivante, après recueil de nouvelles suggestions, sera la bascule vers une version 0.9 qui décrira la quasi-totalité des caractéristiques, avant un ultime polissage aboutissant à la version 1.0.

Les points principaux de la version préparatoire 0.7 de PCIe 6.0

L'un des points forts sera le doublement de la bande passante par rapport à PCIe 5.0, à 64 GT/s, alors que cette interface double déjà sa bande passante par rapport à PCie 4.0, tout en maintenant une rétrocompatibilité et en intégrant la modulation PAM4 ainsi qu'un mécanisme de connection d'erreur FEC (Forward Error Correction).

Les premiers produits intégrant l'interface PCIe 6.0 ne sont pas pour tout de suite, alors que PCIe 5.0 s'apprête à faire ses premiers pas sur différents marchés (surtout professionnels).