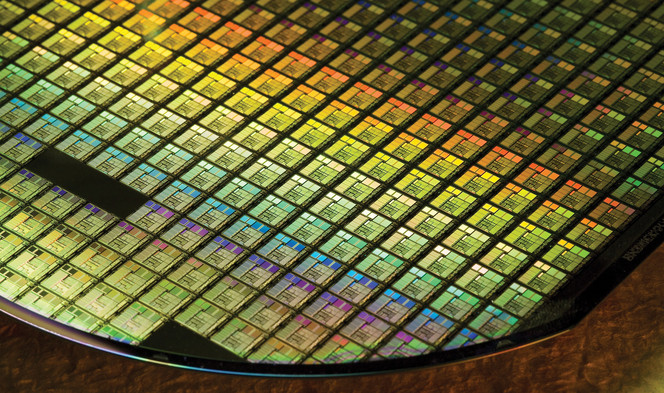

Le fondeur taiwanais TSMC est le leader mondial incontesté de la production de puces et il est parti pour renforcer ses positions ces prochaines années. Déjà détenteur de 54% de part de marché du secteur en revenus en 2021, il devrait continuer de gagner des points pour atteindre 56% cette année, selon le cabinet d'études TrendForce.

Réactif sur le marché pour conserver ses plus gros clients, il impose un rythme d'enfer sur l'évolution des noeuds de gravure. Pour gagner du temps sur la gravure en 3 nm, il a conservé le type de transistor FinFET utilisé précédemment en 5 nm, là où des acteurs comme Samsung passeront à la génération suivante GAAFET (Gate All Around).

Sa gravure en 3 nm de première génération (N3) sera disponible pour de la production de masse dès le troisième trimestre 2022 pour les plus pressés mais il est déjà question de l'évolution N3E, toujours en FinFET et qui arriverait dès le deuxième ou troisième trimestre 2023, et qui constituerait la gravure en 3 nm mature de TSMC.

La gravure en 2 nm pour 2025-2026

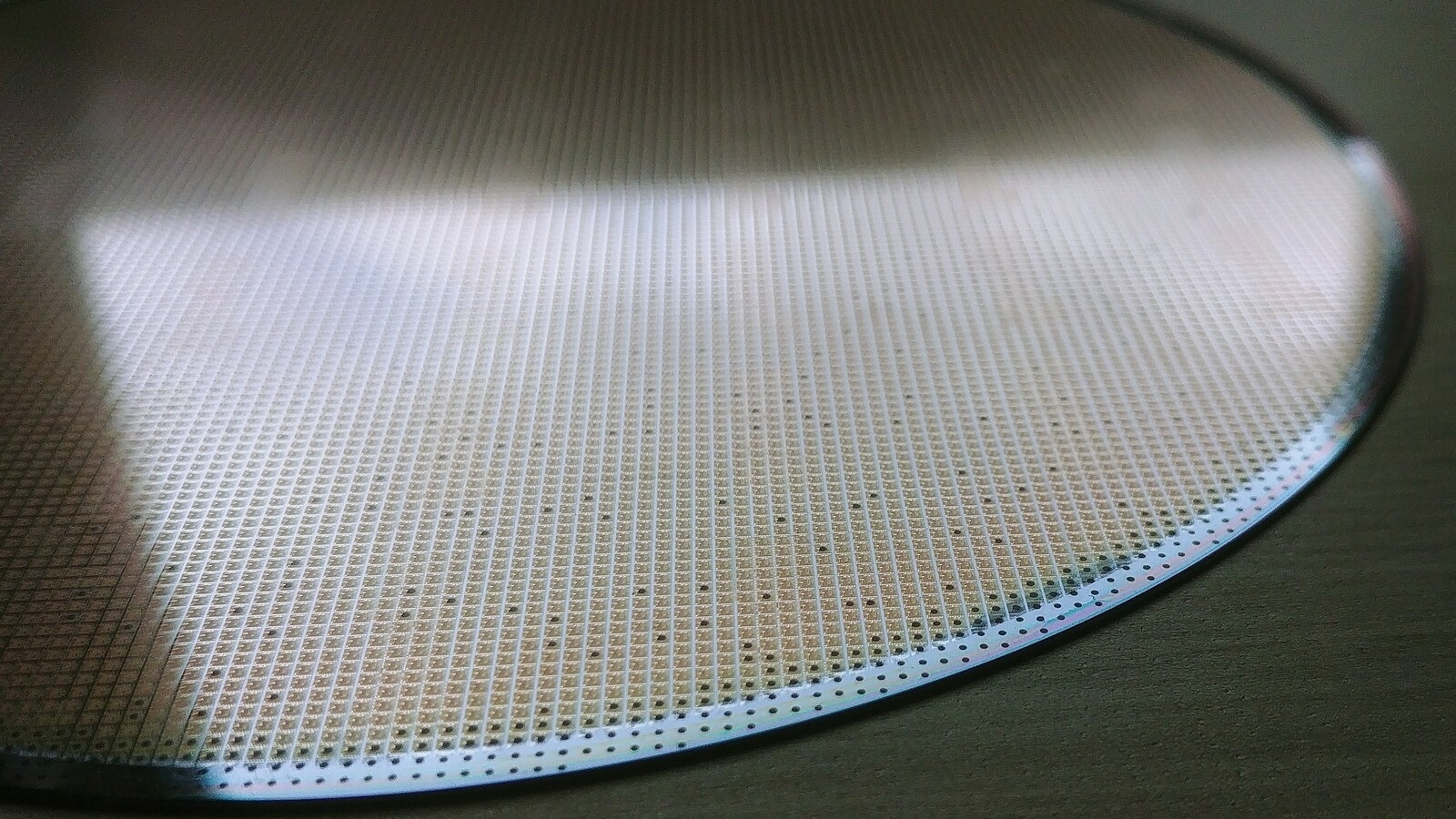

Tout en se félicitant d'être en avance sur son calendrier, le fondeur taiwanais planche déjà sur la gravure en 2 nm (N2) qui passera cette fois au GAAFET et dont on commencera à attendre parler d'ici fin 2024. Ce ne sera toutefois que fin 2025 ou plus sûrement en 2026 que la production de masse sera lancée.

TSMC doit d'abord finaliser un nouveau site à Baoshan (Taiwan), baptisé Fab 20, dont les activités pourront en principe démarrer vers mi-2024, ce qui laisse envisager une pré-production possible dès fin 2024, trois ans après la gravure en 3 nm.

Il reste à voir si le fondeur parviendra à gagner un précieux trimestre sur ses prévisions, ce qui permet généralement d'écarter la concurrence. Apple reste sa priorité numéro un mais le fondeur observe du coin de l'oeil Intel et ses nouvelles ambitions de fondeur pour des clients tiers, et plus particulièrement le calendrier agressif pour le lancement du noeud Intel 18A (équivalent de la gravure en 2 nm) dès 2025, même si sa portée devrait rester limitée.

En restant sur du FinFET tout au long du cycle du noeud N3, TSMC prend un certain risque par rapport aux acteurs qui passeront directement au GAAFET en termes de performances mais sa rapidité d'exécution ainsi que sa flexibilité devront jouer en sa faveur.