Engagé dans une course aux noeuds de gravure toujours plus fins avec le taiwanais TSMC, le groupe Samsung a su intéresser plusieurs acteurs majeurs avec le lancement rapide de sa technologie de gravure 10 nm, comme par exemple Qualcomm et son SoC haut de gamme SnapDragon 835 déjà annoncé dans le Sony Xperia XZ Premium et attendu dans les futurs Galaxy S8 / S8+ de Samsung, pour commencer.

Déjà, la firme annonce le calendrier des prochaines évolutions, avec la gravure 10 nm LPP (Low Power Plus) prévue pour la fin de l'année et la gravure 10 nm LPU (Low Power Ultimate) attendue en 2018.

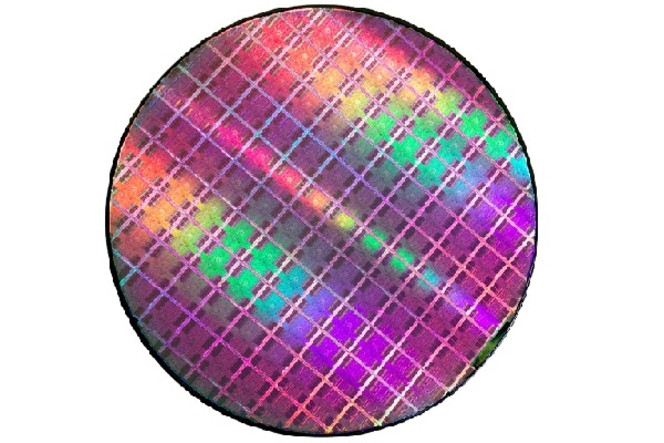

Samsung annonce avoir déjà écoulé plus de 70 000 wafers gravés en 10 nm LPE depuis le démarre de la production de masse en octobre 2016. Dans le même temps, le fabricant de semiconducteurs se prépare aussi à passer à la gravure 7 nm FinFET qui devrait débuter en 2018/2019 et apportera encore plus de réduction de consommation d'énergie et de compacité des processeurs.

Dans le même temps, Samsung annonce vouloir proposer des variations avec de la gravure en 8 nm puis en 6 nm. Ces deux noeuds profiteront des avancées réalisées sur les technologies 10 nm et 7 nm et pourront répondre à des besoins spécifiques, tout en offrant des coûts attractifs.

Samsung détaillera les technologies et la roadmap des noeuds 8 nm et 6 nm lors d'un événement dédié au mois de mai 2017.