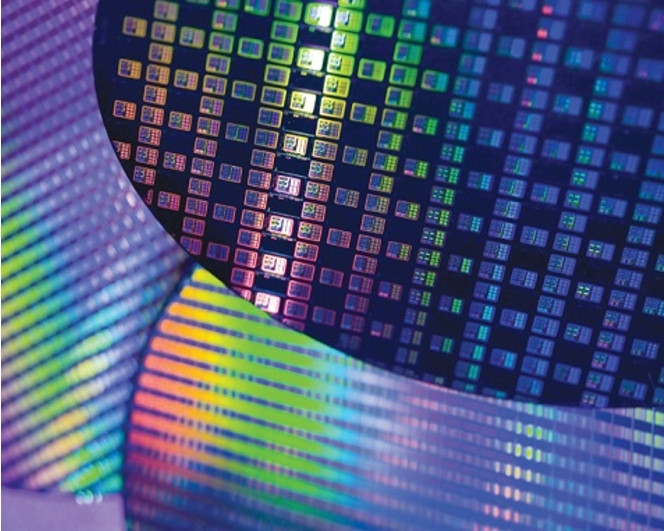

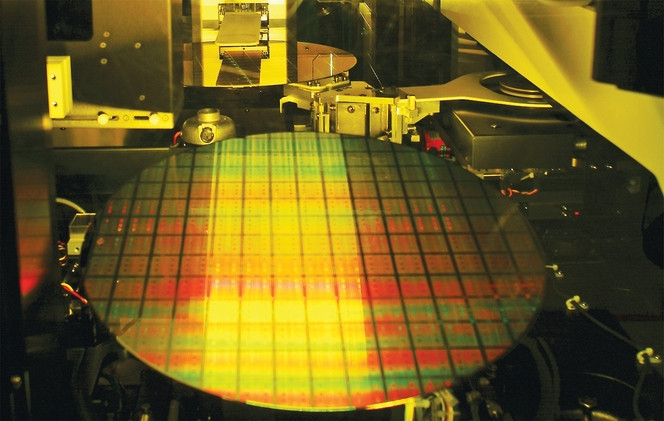

les fondeurs TSMC et Samsung proposent désormais de la gravure en 7 nm pour des composants toujours plus puissants et économes en énergie, avant de la faire évoluer vers du 6 et du 5 nm.

Pour passer au noeud 3 nm, il faudra changer de technologie pour s'accommoder des contraintes grandissantes de la finesse de gravure. Cette migration fera de nouveau l'objet d'une féroce bataille économique entre les différents acteurs, le premier à la proposer permettant souvent d'engranger les clients et d'imposer son rythme à ses concurrents.

Au mois de mai, le groupe Samsung avait annoncé avoir réalisé les premières avancées significatives dans ce domaine en proposant un premier PDK (Product Design Kit) qui permet déjà à de potentiels clients de réaliser des travaux préparatoires autour de la gravure en 3 nm.

Le fondeur taiwanais TSMC, qui a déjà su s'imposer sur le 7 nm, entend bien avancer rapidement lui aussi vers la gravure en 3 nm et assure que le développement des nouvelles techniques avance bien, permettant déjà de capter l'attention de futurs clients.

Contrairement à Samsung qui évoque déjà la piste du GAA MBCFET en remplacement de l'actuel FinFET, TSMC ne donne pas d'informations sur la technique choisie, mais la firme espère bien prolonger son leadership actuel sur le prochain noeud de gravure, ce qui devrait conduire à des développements soutenus.